In quantum computing, the accuracy and reliability of gate operations define the boundary between experimental performance and practical utility. Gate fidelity, the measure of how accurately a quantum gate performs its intended transformation, is one of the most critical metrics in evaluating qubit systems. Erik Hosler, a semiconductor engineering advocate for scalable quantum integration, emphasizes how the foundation of gate fidelity begins not only with quantum logic but with the precision of materials, fabrication and design at the semiconductor level.

Improving gate fidelity demands more than better algorithms or theoretical constructs. It requires deep coordination between quantum physicists, device engineers and foundry technologists who understand how fabrication variables influence error rates, coherence times and quantum behavior under real operating conditions.

Why Gate Fidelity Matters in Quantum Systems

Quantum gates operate by manipulating quantum states through controlled pulses, whether electrical, optical or magnetic. Each operation, whether a single qubit rotation or a two-qubit entanglement gate, must be performed with minimal deviation from the ideal. Even small imperfections can introduce errors that accumulate rapidly as the number of operations increases.

In practical quantum computing, especially with fault-tolerant architectures, maintaining gate fidelity above certain thresholds is essential. For many quantum error correction schemes, such as surface codes, fidelity must exceed 99 percent to allow meaningful scaling. Falling short of these thresholds results in too much overhead for error correction to function efficiently. Any noise, drift or structural inconsistency at the semiconductor level can degrade gate performance and reduce the viability of a quantum architecture.

Fabrication Tolerances and Quantum Behavior

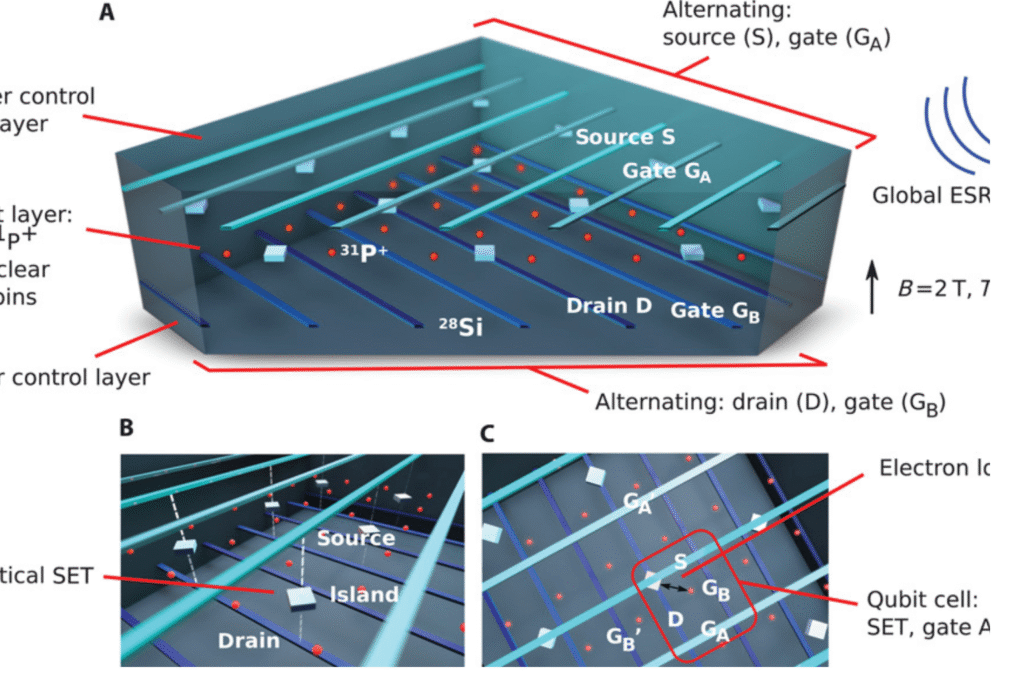

Semiconductor engineering plays a foundational role in achieving high gate fidelity. The uniformity of gate structures, the quality of dielectric layers and the purity of materials all influence how reliably qubits respond to control signals. For example, in superconducting qubits, variations in junction size or barrier thickness can change the energy level spacing, making it harder to calibrate and control gate pulses. In spin qubits, impurities or strain in the substrate can affect magnetic interactions and coherence.

Lithographic precision becomes critical when defining the geometry of qubit elements. Errors at the nanometer scale can cause differences in qubit frequency, coupling strength or crosstalk, all of which reduce gate accuracy. Semiconductor tools are being adapted to meet the precision and uniformity required for quantum devices. Thermal and mechanical stress during fabrication can also shift qubit properties. Engineers must design process flows that minimize stress, prevent contamination and preserve the integrity of sensitive quantum materials throughout the manufacturing process.

Material Purity and Interface Engineering

Gate fidelity also depends on how well materials support coherent quantum states. Charge traps, dislocations and surface roughness all introduce potential sources of decoherence and noise. To reduce variability, semiconductor engineers are exploring ultra-high-purity materials, epitaxial growth methods and defect suppression techniques. Interface engineering is especially important in hybrid quantum devices. For example, semiconductor superconductor interfaces must be atomically clean and structurally aligned to enable coherent coupling. Even minor chemical contamination at these boundaries can degrade gate fidelity.

Dielectric materials used for insulation or gate control must exhibit low-loss tangents and stable properties at cryogenic temperatures. New materials such as crystalline oxides and two-dimensional dielectrics are being investigated for their low decoherence contributions and compatibility with quantum-scale geometries. As Erik Hosler points out, “Working with new materials like GaN, SiC, graphene and other two-dimensional materials is unlocking new potential in semiconductor fabrication, and with it, new semiconductor equipment platforms will likely be required, like accelerator-based light sources.”

Pulse Control and Gate Calibration

Gate fidelity is not just about materials; it also depends on the accuracy of control pulses delivered to each qubit. These pulses must be shaped, timed and directed with high resolution. Cryogenic digital-to-analog converters, fast-switching transistors and low-noise amplifiers are being engineered to deliver precise gate pulses. Errors in pulse amplitude, duration or phase can directly reduce fidelity, so every component in the signal path must operate with tight tolerances.

Calibration routines align gate operations across qubits and over time. These routines depend on accurate metrology and stable electronics, which in turn rely on semiconductor reliability and system-level integration. Without this backbone, even the most sophisticated calibration cannot compensate for hardware drift or noise.

Crosstalk and Isolation in Qubit Arrays

As quantum systems scale to include more qubits, isolating gate operations becomes increasingly difficult. Crosstalk between adjacent qubits or control lines can introduce unintended interactions that lower fidelity. Semiconductor layout plays a critical role in minimizing these effects.

Engineers are using multi-layer routing, on-chip shielding and optimized signal paths to reduce electromagnetic interference and signal overlap. Placement strategies that space out high-activity zones or create buffer regions also help maintain isolation. Crosstalk analysis tools borrowed from classical chip design are being adapted to predict error propagation in qubit arrays. These tools allow designers to simulate gate interactions and adjust layouts before fabrication, preserving fidelity across increasingly complex quantum processors.

Monitoring and Improving Fidelity Post-Fabrication

Once quantum chips are built, semiconductor-based test platforms are used to evaluate gate fidelity in real conditions. Randomized benchmarking, process tomography and interleaved gate tests are applied to assess how closely actual gate operations match their intended outcomes. Test results are fed back into process improvement, guiding future lithography, material selection and design rules.

Semiconductor foundries working on quantum chips are beginning to apply yield and variation analysis to fidelity data, creating feedback loops that resemble those used in classical chip production. These tools are essential for building reliable quantum systems. They allow engineers to identify failure modes, refine device geometries and quantify how changes in materials or process flows affect overall gate performance.

Designing Fidelity into the Quantum Stack

Gate fidelity will continue to be a defining constraint in quantum system design. It influences the choice of qubit modality, architecture, software and error correction. The role of semiconductor engineering is to build a hardware platform that supports high fidelity as a baseline, not as an exception. To do this, engineers must consider fidelity at every level of the device stack, from atomically flat substrates and cleanroom conditions to control electronics and interconnects.

Co-design between device physicists and fabrication experts is becoming standard practice, with shared responsibility for meeting fidelity targets. Automation, metrology and modeling tools are all contributing to a deeper understanding of how design choices propagate through fabrication and into quantum performance. This holistic approach is laying the foundation for scalable, high-fidelity quantum computing platforms.

Enabling Quantum Accuracy Through Engineering Precision

Achieving high gate fidelity is not just a scientific challenge; it is a manufacturing challenge. The same principles that made classical semiconductors reliable: precision, control and feedback are now being applied to quantum systems.

Semiconductor engineering is becoming the enabler of quantum fidelity by ensuring that every qubit behaves as expected, every pulse lands as intended, and every device meets the standards required for practical computing. As the quantum field matures, gate fidelity will increasingly reflect not just physical theory but engineering execution.